Verilog тілінде комбинациялық құрылғыны зерттеу

-

erzhanova_nazym

erzhanova_nazym

- Амалдық жүйелер / 27 наурыз 2015, 22:54

- 79

Құрметті, Достар!!! Мен сіздерге verilog программасында құрылғыны моделдеу жұмысын ұсынамын. Verilog — бұл электронды жүйелерді моделдеуді өңдеу үшін қолданатын аппаратуралық сипаттау тілі.

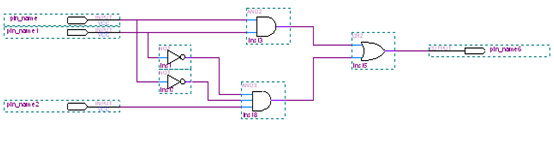

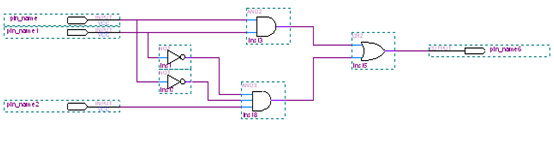

Төменде берілген құрылғыны моделдеу жұмысын ұсынамын.

Келесі алгоритмді жасау арқылы іске асырылады:

1. Мәтіндік редокторды ашамыз. Келесі мәтінді тереміз:

module ExclusiveXOR(x1,x2,x3,f);

input x1,x2,x3;

output f;

assign f = ( x1 & x2 )|( ~x1 & ~x2 & x3 );

endmodule

Файлды .v кеңейтілімімен сақтаймыз;

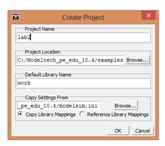

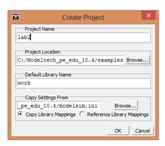

2. ModelSim-да жаңа жоба құрамыз. File->New->project. ProjectName-да атын жазамыз. ОК батырмасын басамыз.

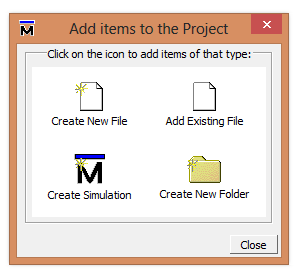

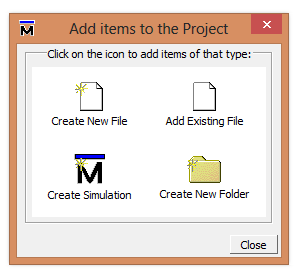

3. 1.v файлын кіргіземіз. Add items to the Project->Add Existing File -> 1.v;

4. 1.v файлына компиляция жасаймыз. Compile ->Compile All;

5. Жұмыс үстелінде мәтіндік редокторды ашамыз. Келесі мәтінді тереміз:

force x1 2#0 0ns, 2#1 100ns;

force x2 2#0 0ns, 2#1 50ns, 2#0 100ns, 2#1 150ns;

force x3 2#0 0ns, 2#1 50ns, 2#0 100ns, 2#1 150ns;

Файлды .do кеңейтілімімен сақтаймыз;

6. Verilog-та 1.do файлды кіргіземіз. Add to Project-> Existing File ->1.do;

7. 1.do файлының оң жағын басып, execute таңдаймыз. Ол файлды орындауға жібереді;

8. Объектерді шығару үшін view ->objects;

9. Simulate -> start Simulation;

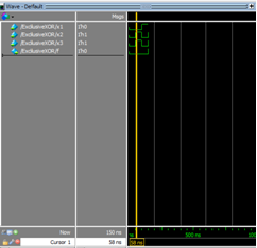

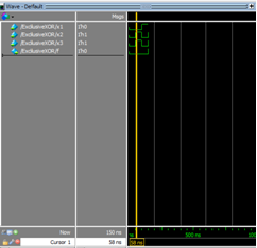

10. Сингалдарды енгіземіз: Add -> To wave ->Signals in Region;

11. Программаны орындауға жібереміз: Simulate -> Run -> Run all;

12. Тексерейік!

x1=0, x2=1, x3=1 f=0.

f = ( x1 & x2 )|( ~x1 & ~x2 & x3 )

a) x1 & x2=0 & 1 = 0;

b) ~x1=~0=1;

c) ~x2=~1=0;

d) ~x1 & ~x2 & x3 = 1 & 0 & 1 = 0;

e) ( x1 & x2 )|( ~x1 & ~x2 & x3 ) = 0 | 0 = 0;

f) f=0.

Төменде берілген құрылғыны моделдеу жұмысын ұсынамын.

Келесі алгоритмді жасау арқылы іске асырылады:

1. Мәтіндік редокторды ашамыз. Келесі мәтінді тереміз:

module ExclusiveXOR(x1,x2,x3,f);

input x1,x2,x3;

output f;

assign f = ( x1 & x2 )|( ~x1 & ~x2 & x3 );

endmodule

Файлды .v кеңейтілімімен сақтаймыз;

2. ModelSim-да жаңа жоба құрамыз. File->New->project. ProjectName-да атын жазамыз. ОК батырмасын басамыз.

3. 1.v файлын кіргіземіз. Add items to the Project->Add Existing File -> 1.v;

4. 1.v файлына компиляция жасаймыз. Compile ->Compile All;

5. Жұмыс үстелінде мәтіндік редокторды ашамыз. Келесі мәтінді тереміз:

force x1 2#0 0ns, 2#1 100ns;

force x2 2#0 0ns, 2#1 50ns, 2#0 100ns, 2#1 150ns;

force x3 2#0 0ns, 2#1 50ns, 2#0 100ns, 2#1 150ns;

Файлды .do кеңейтілімімен сақтаймыз;

6. Verilog-та 1.do файлды кіргіземіз. Add to Project-> Existing File ->1.do;

7. 1.do файлының оң жағын басып, execute таңдаймыз. Ол файлды орындауға жібереді;

8. Объектерді шығару үшін view ->objects;

9. Simulate -> start Simulation;

10. Сингалдарды енгіземіз: Add -> To wave ->Signals in Region;

11. Программаны орындауға жібереміз: Simulate -> Run -> Run all;

12. Тексерейік!

x1=0, x2=1, x3=1 f=0.

f = ( x1 & x2 )|( ~x1 & ~x2 & x3 )

a) x1 & x2=0 & 1 = 0;

b) ~x1=~0=1;

c) ~x2=~1=0;

d) ~x1 & ~x2 & x3 = 1 & 0 & 1 = 0;

e) ( x1 & x2 )|( ~x1 & ~x2 & x3 ) = 0 | 0 = 0;

f) f=0.

-

+2

0 пікір