Verilog HDL тілі

-

venera1

venera1

- Амалдық жүйелер / 2 наурыз 2015, 11:09

- 3427

Салем достар!!! Сіздердің назарларыңызға Verilog тілінің жалпы түсініктемесін жазып кеткім келеді.

Verilog, Verilog HDL (англ. Verilog Hardware Description Language) — бұл аппаратураны сипаттау тілі.Ол цифрлік микросхемаларды верификациялау, модельдеу жіне проекттеу үшін қолданылады. Verilog always процесс блогын ұсынады, ол контекстке байланысты аппаратураның әр түрлі типтерін сипаттайды.Блоктайтын айнымалылар бір процестің ағынын синхронизациялау үшін қолданылады.Verilog тілінде екі түрлі меншіктеу операторлары қолданылады: блоктайтын(=) және блоктамайтын( Verilog HDL- ды VHDL – мен шатыстырмау керек.

VHDL (ағылш. VHSIC (Very high speed integrated circuits) Hardware Description Language) — интегралды микросхемалар аппаратурасын сипаттау тілі. VHDL тілі қазіргі кездегі еспетеу жүйелерінің аппаратурасын жасау барысында негізгі тіл болып табылады.

Бірінші кездерде бұл тіл модельдеу үшін арналған, бірақ кейінірек синтез үшін де жарамды болды. VHDL құралдарымен әр түрлі абстракция деңгейлерінде (құрылымдық, регистрлік тасымалдау, алгоритмикалық) жобалау мүмкіндігін береді. Иерархиялық жобалау мүмкіндігі де бар. Осы тілдің үш құрама бөлігін бөліп көрсетуге болады: алгоритмикалық — Ada және Pascal тілдеріне негізделген, бұл VHDL тіліне программалау тілдері қасиеттерін береді; мәселелік бақытталған – аппаратураны сипаттау тілі қасиетін беретін болмысы; объектілі-бағытталған – қазіргі уақытта қарқынды дамуда [6, 576].

VHDL тілінің стандарттары: 1987, 1991, 1993, 1996, 1997, 1999, 2000 және 2002 жж.

VHDL сандық микросхемаларды сипаттау үшін құрылған, бірақ оның аналогты және сандық-аналогты схемаларды сипаттауға арналған VHDL AMS (Analog Mixed Signal) түрі де бар [7, 252].

Негізінен, VHDL-дан басқа аппаратураны сипаттау тілдері қазір көп. Олардың кең тарағандары: Verilog, SystemC, AHDL, Superlog, SystemVerilog6 UDL/I, VITAL.

Verilog – ты құрушылар оның синтаксисін С++ тіліне ұқсас етіп жасаған. Verilog тілінде жазылған аппаратура сипаттамасын программа деп атайды, бірақ программа деген мағына мұнда жүйенің құрылымын көрсетеді. Сонымен қатар Verilog тілінде «Программаның орындалуы» деген термин қолданылмайды.

Даму тарихы

Verilog 1983-1984 жылы қыста Automated Integrated Design Systems фирмасында аппаратураны модельдеу тілі ретінде Phil Moorby мен Prabhu Goel құрған. 1990 жылы Gateway Design Automation Cadence Design Systems-те сатып алынды. Cadence компаниясының Gateway’s Verilog и Verilog-XL simulator логикалық симуляторларына құқығы бар.

Verilog-95

VHDL тілі кең таралған соң, Cadence компаниясы тілдің стандартизациясына жеткісі келді. Verilog IEEE-ге IEEE 1364—1995 деп аталатын стандарт ретінде жіберілді.( Verilog-95)

Verilog 2001

Verilog-95 тіліне қосымша ретінде IEEE 1364—2001 (немесе Verilog-2001). Тағайындалды.

Verilog-2001 Verilog-95-тің жаңартылған версиясы. Біріншіден, ол белгі айнымалыларын қолдайды, файлдық енгізу – шығару жақсартылды. Синтаксисі өзгерді.

Verilog 2005

Verilog 2005 (стандарт IEEE 1364—2005) үлкен емес өзгертулер енгізді, спецификациялар мен жаңа синтаксистік конструкциялар қосылды.Мысалы: uwire кілттік сөзі

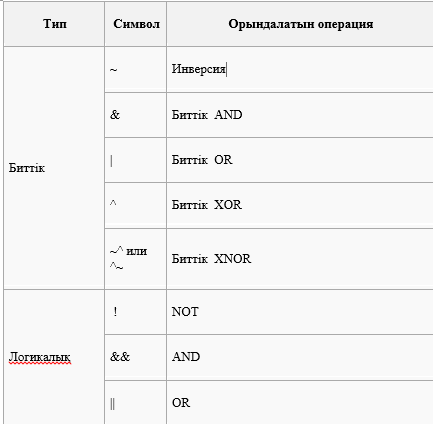

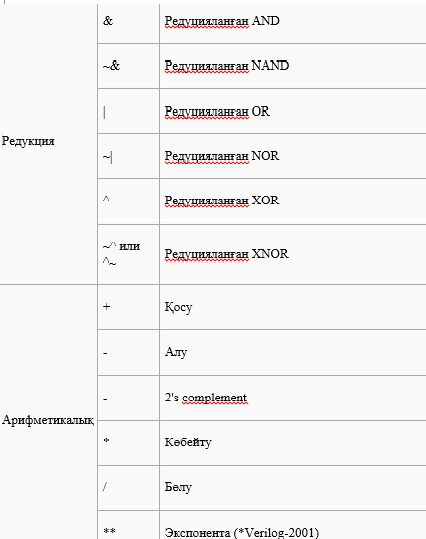

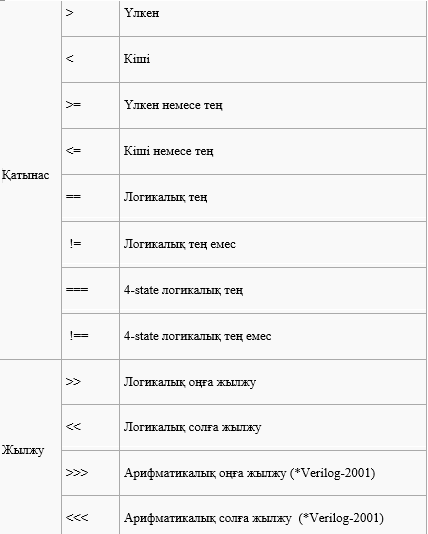

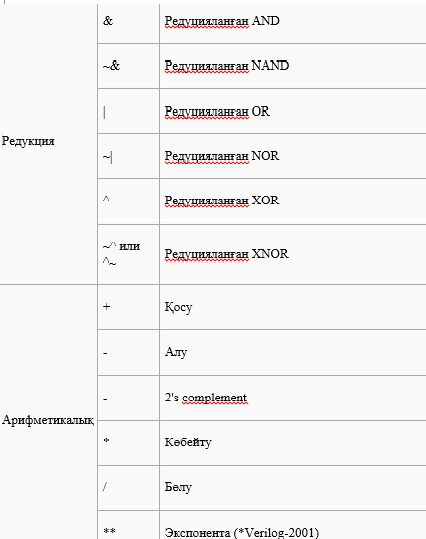

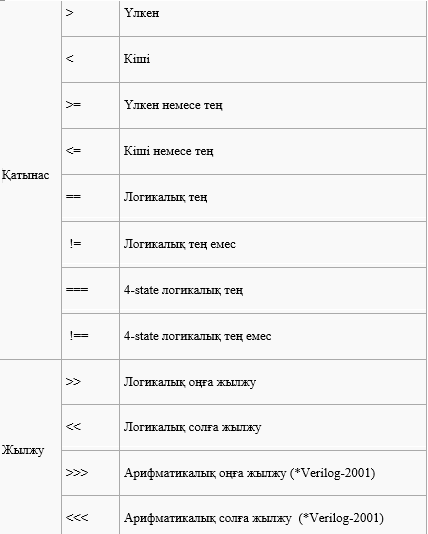

Verilog тілінің кейбір операциялары.

Verilog, Verilog HDL (англ. Verilog Hardware Description Language) — бұл аппаратураны сипаттау тілі.Ол цифрлік микросхемаларды верификациялау, модельдеу жіне проекттеу үшін қолданылады. Verilog always процесс блогын ұсынады, ол контекстке байланысты аппаратураның әр түрлі типтерін сипаттайды.Блоктайтын айнымалылар бір процестің ағынын синхронизациялау үшін қолданылады.Verilog тілінде екі түрлі меншіктеу операторлары қолданылады: блоктайтын(=) және блоктамайтын( Verilog HDL- ды VHDL – мен шатыстырмау керек.

VHDL (ағылш. VHSIC (Very high speed integrated circuits) Hardware Description Language) — интегралды микросхемалар аппаратурасын сипаттау тілі. VHDL тілі қазіргі кездегі еспетеу жүйелерінің аппаратурасын жасау барысында негізгі тіл болып табылады.

Бірінші кездерде бұл тіл модельдеу үшін арналған, бірақ кейінірек синтез үшін де жарамды болды. VHDL құралдарымен әр түрлі абстракция деңгейлерінде (құрылымдық, регистрлік тасымалдау, алгоритмикалық) жобалау мүмкіндігін береді. Иерархиялық жобалау мүмкіндігі де бар. Осы тілдің үш құрама бөлігін бөліп көрсетуге болады: алгоритмикалық — Ada және Pascal тілдеріне негізделген, бұл VHDL тіліне программалау тілдері қасиеттерін береді; мәселелік бақытталған – аппаратураны сипаттау тілі қасиетін беретін болмысы; объектілі-бағытталған – қазіргі уақытта қарқынды дамуда [6, 576].

VHDL тілінің стандарттары: 1987, 1991, 1993, 1996, 1997, 1999, 2000 және 2002 жж.

VHDL сандық микросхемаларды сипаттау үшін құрылған, бірақ оның аналогты және сандық-аналогты схемаларды сипаттауға арналған VHDL AMS (Analog Mixed Signal) түрі де бар [7, 252].

Негізінен, VHDL-дан басқа аппаратураны сипаттау тілдері қазір көп. Олардың кең тарағандары: Verilog, SystemC, AHDL, Superlog, SystemVerilog6 UDL/I, VITAL.

Verilog – ты құрушылар оның синтаксисін С++ тіліне ұқсас етіп жасаған. Verilog тілінде жазылған аппаратура сипаттамасын программа деп атайды, бірақ программа деген мағына мұнда жүйенің құрылымын көрсетеді. Сонымен қатар Verilog тілінде «Программаның орындалуы» деген термин қолданылмайды.

Даму тарихы

Verilog 1983-1984 жылы қыста Automated Integrated Design Systems фирмасында аппаратураны модельдеу тілі ретінде Phil Moorby мен Prabhu Goel құрған. 1990 жылы Gateway Design Automation Cadence Design Systems-те сатып алынды. Cadence компаниясының Gateway’s Verilog и Verilog-XL simulator логикалық симуляторларына құқығы бар.

Verilog-95

VHDL тілі кең таралған соң, Cadence компаниясы тілдің стандартизациясына жеткісі келді. Verilog IEEE-ге IEEE 1364—1995 деп аталатын стандарт ретінде жіберілді.( Verilog-95)

Verilog 2001

Verilog-95 тіліне қосымша ретінде IEEE 1364—2001 (немесе Verilog-2001). Тағайындалды.

Verilog-2001 Verilog-95-тің жаңартылған версиясы. Біріншіден, ол белгі айнымалыларын қолдайды, файлдық енгізу – шығару жақсартылды. Синтаксисі өзгерді.

Verilog 2005

Verilog 2005 (стандарт IEEE 1364—2005) үлкен емес өзгертулер енгізді, спецификациялар мен жаңа синтаксистік конструкциялар қосылды.Мысалы: uwire кілттік сөзі

Verilog тілінің кейбір операциялары.

-

+8